반도체 제조에서 증착은 실리콘 웨이퍼 위에 재료의 박막을 입히는 기본적인 공정입니다. 이는 마이크로칩의 복잡하고 다층적인 구조를 쌓아 올리는 첨가 공정을 의미합니다. 패턴을 만들기 위해 재료를 제거하는 감산 공정인 에칭과는 직접적으로 대조됩니다.

증착은 단일 작업이 아니라 원자층 단위로 칩을 구성하는 고도로 제어된 기술의 범주입니다. 선택된 특정 방법(화학적 또는 물리적)은 최종 반도체 장치의 성능, 신뢰성 및 비용을 직접적으로 결정하는 중요한 엔지니어링 결정입니다.

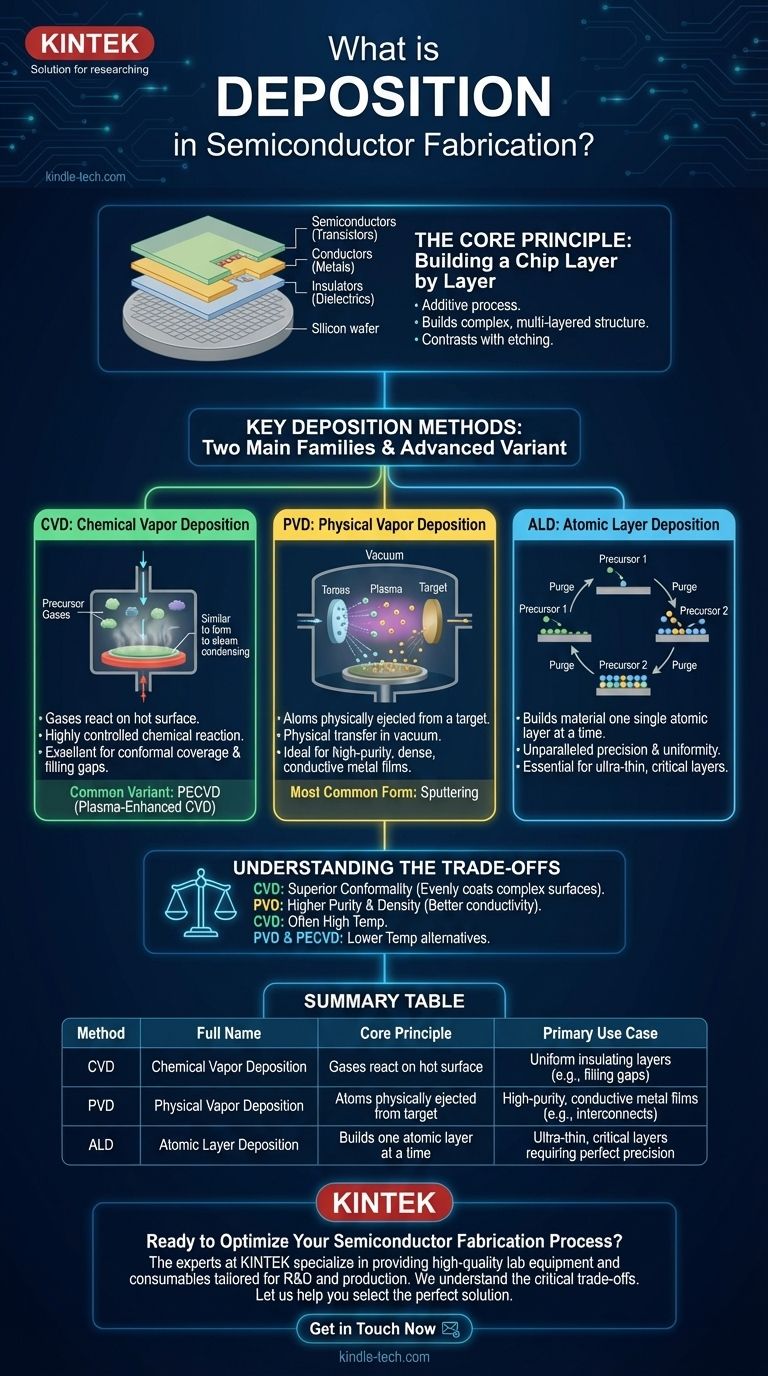

핵심 원리: 칩을 층별로 구축하기

현대 마이크로프로세서는 수십억 개의 부품으로 이루어진 믿을 수 없을 정도로 복잡한 미세한 고층 빌딩과 같습니다. 증착은 각 층과 그 사이의 배선을 구축하는 데 사용되는 공정입니다.

첨가 공정

실리콘 웨이퍼를 건물의 기초라고 생각해보세요. 증착은 그 기초 위에 새로운, 완벽하게 균일한 재료 층을 추가하는 과정입니다. 이것은 절연층, 전도성 금속 또는 다른 반도체 재료일 수 있습니다.

증착된 층의 목적

각 증착된 층은 특정 기능을 수행합니다.

- 실리콘 이산화물(SiO₂)과 같은 절연체(유전체)는 다른 부품 간에 전류가 새는 것을 방지합니다.

- 구리 또는 알루미늄과 같은 도체는 칩 주변으로 신호를 전달하는 "전선" 또는 상호 연결을 형성합니다.

- 폴리실리콘과 같은 반도체는 모든 디지털 논리의 기초가 되는 온/오프 스위치인 트랜지스터 자체를 만드는 데 사용됩니다.

주요 증착 방법: 두 가지 주요 계열

엔지니어들은 이러한 층을 증착하기 위해 두 가지 주요 기술 계열을 사용하며, 각각 고유한 장점과 사용 사례를 가지고 있습니다. 선택은 증착될 재료와 최종 장치에서 수행할 역할에 전적으로 달려 있습니다.

화학 기상 증착 (CVD)

CVD에서 웨이퍼는 챔버에 놓이고 하나 이상의 휘발성 전구체 가스에 노출됩니다. 이 가스들은 웨이퍼의 뜨거운 표면에서 반응하거나 분해되어 원하는 고체 막을 생성합니다.

이는 증기가 차가운 창문에 응결되어 물 층을 형성하는 것과 유사하지만, 액체 대신 고체 막을 생성하는 고도로 제어된 화학 반응입니다. 플라즈마 강화 CVD (PECVD)는 저온에서 이러한 반응을 가능하게 하기 위해 플라즈마를 사용하는 일반적인 변형입니다.

물리 기상 증착 (PVD)

PVD에서 증착될 재료는 고체 타겟으로 시작됩니다. 이 타겟은 진공 상태에서 고에너지 이온(일반적으로 아르곤 플라즈마에서 나옴)에 의해 충격을 받아 타겟에서 원자가 물리적으로 떨어져 나옵니다.

이러한 방출된 원자들은 진공을 통해 이동하여 웨이퍼를 코팅합니다. PVD의 가장 일반적인 형태는 스퍼터링으로, "모래"(방출된 원자)가 쌓여 웨이퍼에 새로운 층을 형성하는 일종의 원자 규모 샌드블라스팅으로 시각화할 수 있습니다.

원자층 증착 (ALD)

가장 진보된 응용 분야의 경우, 원자층 증착(ALD)은 비할 데 없는 정밀도를 제공합니다. 이는 말 그대로 한 번에 단일 원자층씩 재료를 쌓아 올리는 CVD 공정의 한 유형으로, 완벽한 균일성과 두께 제어를 제공합니다.

장단점 이해하기

CVD와 PVD 사이의 선택은 임의적이지 않습니다. 이는 층의 요구 사항에 기반한 중요한 엔지니어링 절충입니다.

균일한 커버리지

CVD 공정은 일반적으로 균일성, 즉 복잡한 3차원 표면을 고르게 코팅하는 능력에서 우수합니다. 반응물 가스가 반응하기 전에 미세한 트렌치와 구멍으로 흘러 들어갈 수 있기 때문에 균일한 층을 생성하며, 이는 밀집된 전선 사이를 절연하는 데 필수적입니다.

순도 및 밀도

PVD는 화학적 공정이 아닌 물리적 전달 공정이기 때문에 금속 막을 증착하는 데 종종 선호됩니다. 이는 더 높은 순도와 밀도를 가진 막을 생성하여 더 나은 전기 전도성으로 이어질 수 있습니다.

온도 및 손상

기존 CVD 공정은 화학 반응을 유도하기 위해 매우 높은 온도를 필요로 하는 경우가 많습니다. 이러한 온도는 칩에 이전에 제조된 층을 손상시킬 수 있습니다. PVD 및 PECVD는 훨씬 낮은 온도에서 작동할 수 있기 때문에 귀중한 대안입니다.

목표에 맞는 올바른 선택

증착 방법은 항상 칩 아키텍처 내에서 특정 기능을 수행하도록 선택됩니다.

- 금속 라인 사이에 절연층을 만드는 것이 주요 초점이라면: 우수한 틈새 채우기 능력과 균일한 커버리지를 위해 CVD(예: PECVD) 형태를 사용할 가능성이 높습니다.

- 금속 배선(상호 연결)을 증착하는 것이 주요 초점이라면: 고순도, 고밀도, 고전도성 막을 만들기 위해 PVD(스퍼터링)를 사용할 가능성이 높습니다.

- 트랜지스터의 초박형, 중요 게이트 산화물을 만드는 것이 주요 초점이라면: 필요한 원자 수준의 정밀도와 완벽함을 달성하기 위해 원자층 증착(ALD)을 사용해야 합니다.

궁극적으로 증착을 마스터하는 것은 칩이 만들어지는 바로 그 과정이기 때문에 전체 반도체 산업에 필수적입니다.

요약표:

| 방법 | 전체 이름 | 핵심 원리 | 주요 사용 사례 |

|---|---|---|---|

| CVD | 화학 기상 증착 | 뜨거운 웨이퍼 표면에서 가스가 반응하여 고체 막을 형성합니다. | 균일한 절연층(예: 틈새 채우기)에 탁월합니다. |

| PVD | 물리 기상 증착 | 타겟에서 원자가 물리적으로 방출되어 웨이퍼를 코팅합니다. | 고순도, 전도성 금속 막(예: 상호 연결)에 이상적입니다. |

| ALD | 원자층 증착 | 한 번에 하나의 원자층씩 재료를 구축하는 CVD 변형입니다. | 완벽한 정밀도를 요구하는 초박형, 중요 층에 필수적입니다. |

반도체 제조 공정을 최적화할 준비가 되셨습니까?

올바른 증착 기술을 선택하는 것은 장치의 성능과 수율에 매우 중요합니다. KINTEK의 전문가들은 반도체 R&D 및 생산의 정밀한 요구 사항에 맞춰 고품질 실험실 장비 및 소모품을 제공하는 데 특화되어 있습니다.

저희는 CVD, PVD, ALD 사이의 중요한 장단점을 이해하고 있습니다. 절연 유전체를 증착하든 고전도성 금속 상호 연결을 증착하든, 귀하의 특정 응용 분야에 완벽한 솔루션을 선택하도록 도와드리겠습니다.

저희 솔루션이 귀하의 실험실 역량을 강화하고 혁신을 추진하는 데 어떻게 도움이 될 수 있는지 논의하려면 오늘 저희 팀에 문의하십시오.

시각적 가이드