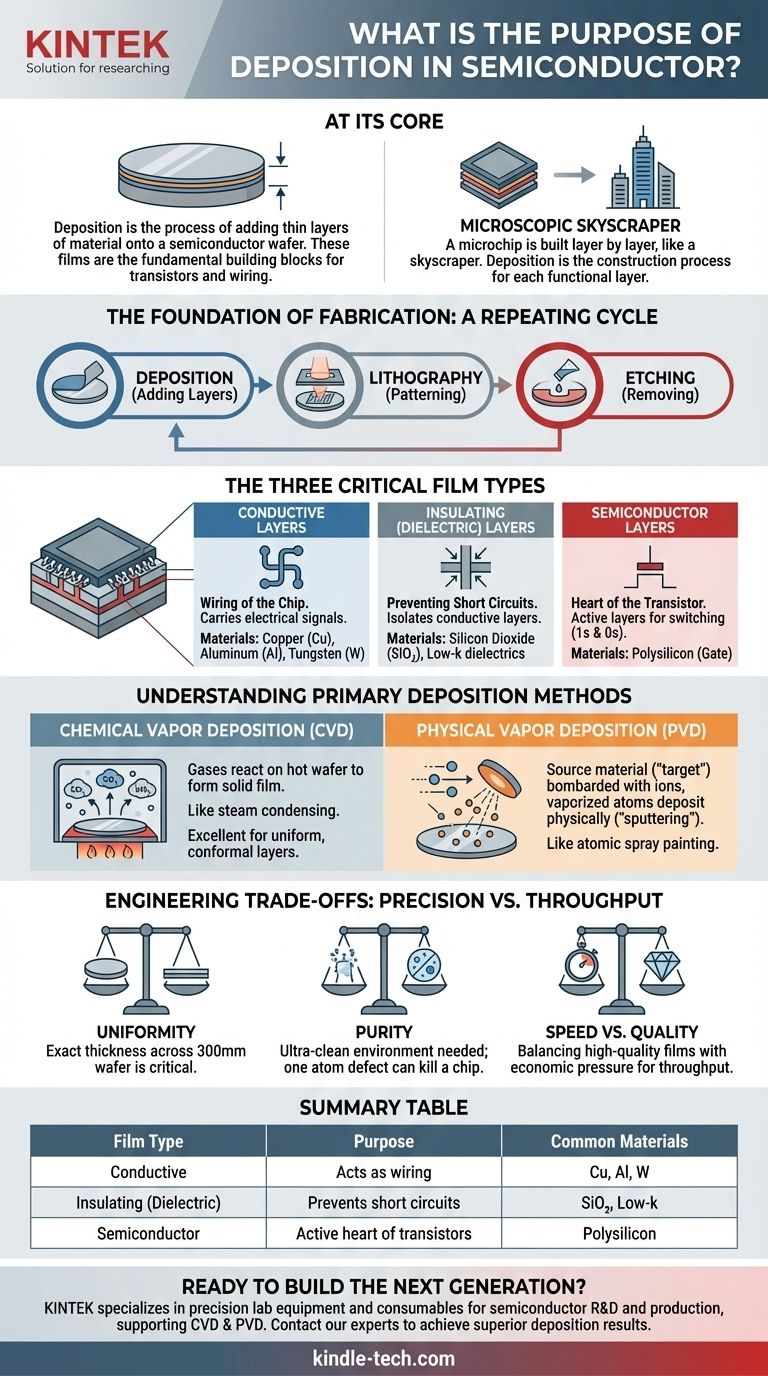

본질적으로 증착은 반도체 웨이퍼 위에 얇은 재료 층을 추가하는 공정입니다. 종종 원자 몇 개 두께에 불과한 이러한 박막은 트랜지스터, 커패시터 및 이들을 연결하는 배선을 형성하는 복잡한 3차원 구조를 구축하는 데 사용되는 기본 구성 요소입니다. 증착이 없다면 실리콘 웨이퍼는 빈 캔버스로 남아 있게 되며 집적 회로의 생성은 불가능할 것입니다.

마이크로칩은 단일 블록에서 조각되는 것이 아니라 미세한 고층 빌딩처럼 층층이 쌓아 올려집니다. 증착은 전도성, 절연성 또는 반도체성 등 이러한 기능성 층 각각을 추가하는 근본적인 구축 공정입니다.

제조의 기반: 층층이 구축하기

마이크로칩 제조를 재료를 깎아내는 조각이 아니라 매우 정밀한 3D 프린팅의 한 형태로 생각해 보십시오. 이 공정은 웨이퍼라고 불리는 깨끗한 원형 실리콘 디스크에서 시작되며, 이것이 기반 역할을 합니다.

전체 제조 공정은 층 추가(증착), 패턴 형성(리소그래피), 선택적 부분 제거(식각)의 반복적인 주기로 이루어집니다. 증착은 이 주기의 중요한 첫 단계로, 칩 아키텍처의 각 새로운 레벨에 대한 원료를 생성합니다.

반도체에서 중요한 세 가지 박막 유형

증착은 단 하나의 재료 유형만 추가하는 것이 아닙니다. 그 목적은 칩 기능에서 특정 역할을 수행하는 고유한 전기적 특성을 가진 다양한 박막을 깔아 놓는 것입니다.

전도성 층: 칩의 배선

이러한 박막은 칩의 다른 구성 요소 간에 전기 신호를 전달하는 미세한 와이어 및 상호 연결 역할을 합니다.

구리(Cu), 알루미늄(Al), 텅스텐(W)과 같은 재료가 증착되어 전류가 흐르는 경로를 만듭니다. 이러한 전도성 층이 없으면 트랜지스터는 서로 통신할 방법이 없는 고립된 섬이 될 것입니다.

절연체(유전체) 층: 단락 방지

이러한 박막은 전기 절연체, 즉 전기를 전도하지 않습니다. 주요 임무는 전도성 층이 서로 분리되도록 하는 것입니다.

이산화규소(SiO2) 또는 더 진보된 저유전율(low-k) 유전체와 같은 재료가 사용됩니다. 이는 신호가 "단락"되거나 서로 간섭하는 것을 방지하며, 이는 수백억 개의 트랜지스터가 작은 영역에 밀집되어 있을 때 매우 중요합니다.

반도체 층: 트랜지스터의 심장

이들은 트랜지스터에 켜고 끄는 기능을 부여하는 "활성" 층으로, 디지털 논리의 1과 0을 나타냅니다.

폴리실리콘과 같은 재료를 증착하는 것은 전류 흐름을 제어하는 부품인 트랜지스터의 게이트를 형성하는 데 필수적입니다. 이러한 증착된 반도체 박막의 정확한 특성은 칩의 성능과 전력 효율을 직접적으로 결정합니다.

주요 증착 방법 이해하기

요구되는 정밀도를 달성하기 위해 엔지니어는 각각 고유한 장점을 가진 두 가지 주요 증착 기술군을 사용합니다.

화학 기상 증착(CVD)

CVD에서는 웨이퍼를 챔버에 넣고 하나 이상의 반응성 가스에 노출시킵니다. 이 가스들은 뜨거운 웨이퍼 표면에서 반응하여 부산물로 원하는 재료의 고체 박막을 남깁니다.

차가운 창문에 김이 서리는 것과 비슷하지만, 물 대신 화학 반응을 통해 단단하고 초순수한 박막이 형성됩니다. CVD는 복잡한 3D 구조를 균일하게 덮는 매우 균일하고 순응성 있는 층을 만드는 데 탁월합니다.

물리 기상 증착(PVD)

PVD에서는 소스 재료("타겟")가 고에너지 이온으로 폭격되어 타겟에서 원자가 튀어나오게 됩니다. 이 기화된 원자들은 진공을 통해 이동하여 원자 단위의 스프레이 페인팅과 같은 방식으로 웨이퍼 표면에 물리적으로 증착됩니다.

이 방법은 종종 스퍼터링(sputtering)이라고 불리며, 금속 및 기타 재료를 직접적인 시선(line-of-sight) 방식으로 증착하는 데 매우 효과적입니다.

트레이드오프: 정밀도 대 처리량

증착의 목적은 완벽한 박막을 만드는 것이지만, 이 목표를 달성하려면 중요한 엔지니어링 트레이드오프를 탐색해야 합니다.

균일성의 과제

증착된 박막은 전체 300mm 웨이퍼에 걸쳐 정확히 동일한 두께를 가져야 합니다. 한쪽에서 다른 쪽까지 단 몇 개의 원자라도 변동이 있으면 수십억 개의 트랜지스터가 다르게 작동하여 칩이 실패할 수 있습니다.

순도의 문제

증착된 박막은 예외적으로 순수해야 합니다. 중요한 층에 원치 않는 이물질 원자가 하나라도 있으면 전기적 특성이 변경되어 칩 전체를 망가뜨리는 결함이 발생할 수 있습니다. 이를 위해서는 초고청정 진공 환경이 필요합니다.

속도 대 품질 딜레마

제조업은 비즈니스이며 처리량(시간당 웨이퍼 수)은 비용에 매우 중요합니다. 일반적으로 박막을 더 빨리 증착하면 품질, 균일성 또는 순도가 저하될 수 있습니다. 엔지니어는 고품질 박막의 필요성과 칩을 신속하게 생산해야 하는 경제적 압력 사이에서 끊임없이 균형을 맞춰야 합니다.

목표에 적용하는 방법

증착의 중요성은 반도체 산업 내 특정 초점에 따라 달라집니다.

- 장치 성능에 중점을 두는 경우: 증착된 유전체 박막(예: 게이트 절연체)의 품질이 트랜지스터 속도와 누설 전류를 직접적으로 결정합니다.

- 제조 수율에 중점을 두는 경우: 증착된 층의 균일성과 결함 없는 특성이 웨이퍼당 작동하는 칩의 수를 높이는 가장 중요한 요소입니다.

- 첨단 아키텍처에 중점을 두는 경우: 원자층 증착(ALD)과 같은 새로운 증착 기술은 FinFET 및 GAA(Gate-All-Around)와 같은 복잡한 3D 트랜지스터 구조로의 전환을 가능하게 합니다.

궁극적으로 증착을 이해하는 것은 모든 현대 마이크로칩을 구성하는 데 사용되는 근본적인 언어를 이해하는 것입니다.

요약 표:

| 박막 유형 | 목적 | 일반적인 재료 |

|---|---|---|

| 전도성 | 전기 신호를 위한 배선 역할 | 구리(Cu), 알루미늄(Al), 텅스텐(W) |

| 절연체(유전체) | 전도성 층 간의 단락 방지 | 이산화규소(SiO₂), 저유전율 유전체 |

| 반도체 | 트랜지스터의 활성 심장 형성 | 폴리실리콘 |

차세대 마이크로칩 구축을 준비하고 계십니까? 증착된 박막의 품질은 장치 성능과 제조 수율을 직접적으로 결정합니다. KINTEK은 반도체 R&D 및 생산을 위한 정밀 실험 장비 및 소모품을 전문으로 합니다. 첨단 아키텍처를 개발하든 고수율을 최적화하든, 당사의 솔루션은 CVD 및 PVD와 같은 중요한 공정을 지원합니다. 우수한 증착 결과를 얻는 방법에 대해 논의하려면 지금 전문가에게 문의하십시오.

시각적 가이드

관련 제품

- RF PECVD 시스템 고주파 플라즈마 강화 화학 기상 증착 RF PECVD

- 유기물 증발 접시

- 박막 분광 전기분해 전지

- 측면 창 광학 전해 전기화학 전지

- 실험실용 칼로멜 은염화물 수은 황산 기준 전극